IIS

# Digital baseband GUaRDIAn

Bonded GUaRDIAn ASIC

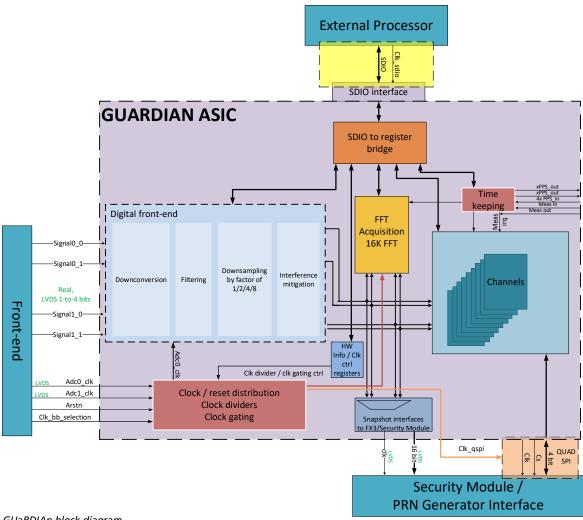

GUaRDIAn is a hardware accelerator chip for Global Navigation Satellite System receivers. It implements the digital baseband processing for interference mitigation, acquisition and correlation of all major GNSS signals available. It accepts up to four digital baseband ADC signals that are preprocessed in a versatile signal condition block followed by interference mitigation. A 16k hardware FFT unit can be used for signal acquisition and interference monitoring. SW-configurable correlator channels are controlled over an external processor interface to enable a multi-functional and versatile GNSS chipset. The receiver control in terms of configuration, acquisition and tracking has to be implemented on an external processor, enabling a variety of different application possibilities.

# **Main Benefits**

- Supports all current and upcoming GNSS signals

- 200 versatile correlator channels for BPSK(n), BOCx(m,n) and AltBOC signals, including complex GNSS signal processing

- Shift-register-based code generators for current GPS, Galileo, BeiDou and GLONASS signals

- Memory channels for current and future memory-code signals

- Multiple digital baseband signal inputs

- Versatile signal conditioning scheme

- FFT based hardware acquisition unit

- Programmable interference mitigation in (combined) time and frequency domain

- Synchronization of several GUaRDIAn chips for a higher number of channels or array processing applications

- Output streaming of processed baseband samples to enable external processing and interference characterization

# Fraunhofer Institute for Integrated Circuits IIS

#### **Executive Director**

Prof. Dr.-Ing. Albert Heuberger Am Wolfsmantel 33 91058 Erlangen Germany

#### Contact

Group Managers Satellite Based Positioning Systems Alexander Rügamer Phone +49 (0) 9 11/5 80 61-6379 Matthias Overbeck Phone +49 (0) 9 11/5 80 61-6368

sls-positioning@iis.fraunhofer.de

Nordostpark 84 90411 Nürnberg Germany

www.iis.fraunhofer.de/positioning

## **Features**

- 200 versatile tracking channels:

- 131 complex 5 tap correlator channels

- 45 memory code channels to be preloaded

- 24 FIFO input channels non-repeatable / externally generated or provided PRN codes

- Support of BOC false peak mitigation correlators

- Fast acquisition module based on 16k point hardware FFT

- Interference mitigation with Pulse Blanker, versatile digital FIR and IIR-Notch-Filters, and Filter Bank Pulse Blanker

- External closure of tracking loops

- Raw data interface, e.g. for a dedicated security module

- 2 xPPS output / 4 xPPS input

GUaRDIAn block diagram

## **Interfaces**

- Up to four ADC input signals; two's complement or sign/mag. with up to 4 bit real or 2 bit I/Q

- QSPI interface to 24 FIFO correlator channels for externally generated/provided PRN-codes

- 16 bit LVDS + clock pre-processed raw data output interface

- SDIO interface / memory mapped to external processor providing configuration interface, correlator I/Q dumps and code/carrier-NCO feedback

# **Technical Details**

- Globalfoundries 55 nm CMOS technology

- Supply: 1.8 V I/O and 1.2 V core

- Die size: 7.12 x 8.12 mm (57,81 mm<sup>2</sup>)